# AQX / AQS

# **RCU Technical Manual**

Version 005

BRUKER

The information in this manual may be altered without notice.

BRUKER accepts no responsibility for actions taken as a result of use of this manual. BRUKER accepts no liability for any mistakes contained in the manual, leading to coincidental damage, whether during installation or operation of the instrument. Unauthorised reproduction of manual contents, without written permission from the publishers, or translation into another language, either in full or in part, is forbidden.

### Verteiler:

#### Änderungshistorie:

| Index: | <u>Datum:</u> | Text:        | <u>Visum:</u> |

|--------|---------------|--------------|---------------|

| 005    | 04.04.2000    | Neu erstellt | RO            |

This manual was written by

Pietro Lendi / Michael Schenkel

© April 11, 2000: Bruker AG

Fällanden, Switzerland P/N: Z31209 DWG-Nr: 876 005

# Contents

|      | Contents                                                                                                     | . 3 |

|------|--------------------------------------------------------------------------------------------------------------|-----|

| 1    | General Infos                                                                                                | . 5 |

| 1.1  | Abbreviation                                                                                                 | 5   |

| 2    | Introduction AQX                                                                                             | . 7 |

| 2.1  | General AQX Version                                                                                          | 7   |

| 2.2  | System overview AQX Version                                                                                  | 8   |

| 2.3  | AQX RCU overview                                                                                             |     |

| 2.4  | AQX Connection to SADC and HADC                                                                              | 11  |

| 2.5  | AQX Connection to FADC                                                                                       | 12  |

| 3    | Introduction AQS                                                                                             | 13  |

| 3.1  | General AQS Version                                                                                          | 13  |

| 3.2  | System overview AQS Version                                                                                  |     |

| 3.3  | AQS RCU overview                                                                                             |     |

| 3.4  | AQS Connection to SADC and HADC                                                                              |     |

| 3.5  | AQS Connection to FADC                                                                                       |     |

| 4    | Installation                                                                                                 | 19  |

| 4.1  | General                                                                                                      | 19  |

| 4.2  | Technical data                                                                                               |     |

| 4.3  | Factory settings                                                                                             |     |

| 4.4  | Assembly motherboard Z3P2886A                                                                                |     |

| 4.5  | Assembly VME logic board Z4P2925B                                                                            |     |

| 4.6  | Jumpersetting                                                                                                |     |

|      | EPROM:                                                                                                       | .21 |

|      | Clock:                                                                                                       | .22 |

|      | DRAM:                                                                                                        | .22 |

|      | VME Interrupt:                                                                                               | .22 |

|      | VME Bus Request:                                                                                             | .23 |

| 4.7  | Programmable logic                                                                                           | 24  |

| 4.8  | Assembly motherboard with extended Memory<br>Modification on the motherboard becauce of 4/8Megx32<br>DRAM 26 | 25  |

| 4.9  | Testprogram                                                                                                  | 27  |

| 4.10 | Configuration Test                                                                                           |     |

|      | Figures                                                                                                      | 29  |

|      | Tables                                                                                                       | 31  |

## Contents

# General Infos

### Abbreviation

- AQBUS --> Acquisition Bus

- AQS --> Acquisition Start ; Acquisition System

- AQX --> Acquisition Unit

- AQR --> Acquisition Rack

- ASU --> Amplitude Setting Unit

- BB--> Broad Band

- CCU --> Communication Control Unit

- DDS --> Direct Digital Synthesizer

- DSP --> Digital Signal Prozessor

- DRAM --> Dynamic Random Access Memory

- EP --> Empfänger Pulse

- EPHD --> Empfänger Puls Homo Decoupling

- EPROM --> Erasable Programmable Read Only Memory

- FADC --> Fast ADC

- FCU --> Frequency Control Unit

- FID--> Free Induction Decay

- FIFO --> First In First Out

- FTLP/4M --> Filter Low Pass / 4MHz

- GCU --> Gradient Control Unit

- HADC/2-->High resolution ADC / 2 (AQR / AQS)

- HR--> **H**igh **R**esolution

- MCI--> Multi Channel Interface

- PAL--> Programmable Array Logic

- PTS--> Program Test Source

- RCP--> Realtime Clock Puls

- RCU --> Receive Control Unit

- SADC --> Standard ADC

- SCI --> Serial Communication Interface

- SPHD --> Sende Pulse Homo Decoupling

1.1

- SRAM --> Static Random Access Memory

- TCU--> Timing Control Unit

- XDWCLK --> Extern DWCLK

- XEP --> Extern EP

# Introduction AQX

### General AQX Version

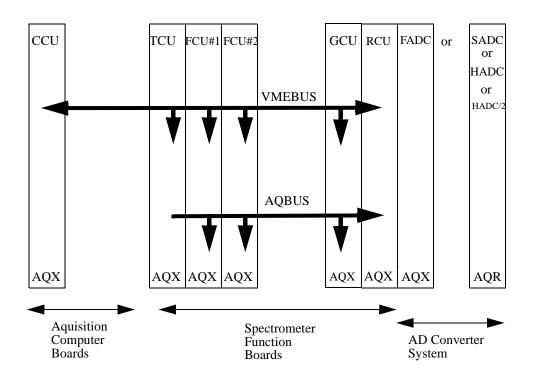

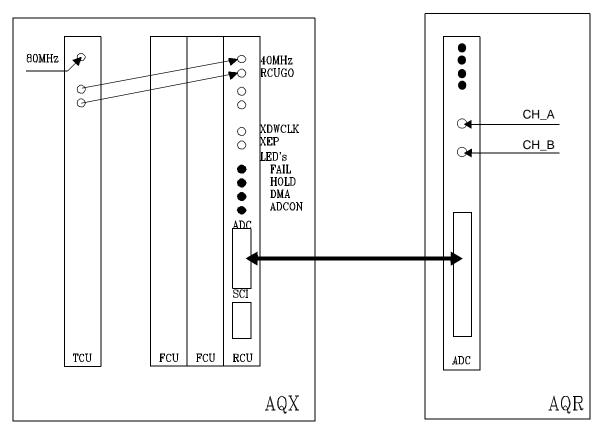

The Receiver Control Unit (RCU) is a member of the aquisition computer AQX. The AQX includes a complete aquisition computer system (i.e. CPU/4 or CCU and the spectrometer specific function boards TCU (Timing Control Unit), FCU (Frequency Control Unit) and the mentioned RCU. The CCU includes also the fast memory and the SIO unit.

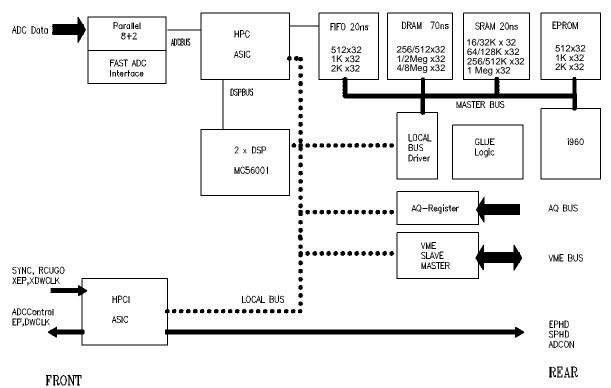

Figure 2.1. Aquisition system

An aditional AQBUS for the spectrometer function boards is used parallel to the VMEBUS. The RCU is the logical master for the AD converter system. It is the receiver of the data from the ADC System.

### System overview AQX Version

The aquisition computer is based on a VME system that uses a 32Bit Processor. So do all spectrometer function boards. Most spectrometer function boards have memory and local processors on board.

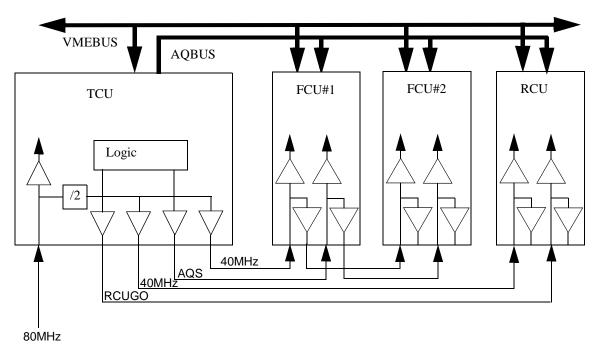

#### Figure 2.2. Spectrometer synchronisation

#### TCU:

The TCU generates most RCP's (realtime clock pulses) for the spectrometer. The main clock for the TCU is 80MHz and is normally feed by a PTS. Based on this clock, the FCU's and the RCU realtime system run synchronous with 40MHz. So the time relation between the transmitter system (TCU, FCU) and the receiver system (RCU) is maintained. In special there are two strobe signals (AQS and RCU-GO), triggering the spectrometer boards.

- 80MHz: This input signal comes directly from the PTS620 and is the clocking frequency for the TCU. The voltage level is 0dBm (0,65Vpp at 50Ω). This signal is used to generate the 40MHz signal.

- 2. **40MHz:** The output signal are TTL (3Vpp at  $50\Omega$ ) and operate on a 50% duty cycle. One is used to clock the FCU's the other to clock the RCU.

- RCUGO: This pulse is used to start the RCU at every scan. It goes high for 50ns.

- AQBUS: Various instructions are sent from TCU to the FCU's (and GCU if fitted) via the Acquisition Bus. This TTL strobe pulse is used to synchronise the timing of the bus. The strobe pulse goes low for a minimum of 25ns.

#### FCU:

- 1. It generates the DDS input for the PTS (frequency and phase).

- 2. It controls the frequency setting of the PTS output.

- 3. It generates MOD, MULT, AT20 and AT40 signals used for power regulation in the ASU boards.

- 4. It controls the phase of the 4 Phase Modulator using ph1 and ph2 signals. In many respects the FCU takes the place of the MCI board.

#### RCU:

- The RCU takes complete control of the acquisition. During the current scan it will operate autonomously until the end of the scan. To perform a second scan however the RCU must wait for a second RCUGO signal from the TCU. The RCUGO signal is synchronised with the 40MHz clock, both are received from the TCU.

- 2. As part of the acquisition control the RCU generates the DWELL CLOCK (DWCLK) as well as the EP and the ADCON signals.

- 3. It is possible to deactivate the internal DWCLK and EP and connect an external DWCLK (XDWCLK) and an EP (XEP) to the RCU.

- 4. The RCU is responsible for processing the acquired data (e.b. digital filtering) as well as accumulation and DMA transfer of processed data to the CCU.

- 5. The RCU is master of all digitizers (SADC, HADC, HADC/2, FADC and HRD16) and all digitizers functions. Also the filter settings (SADC, HADC, HADC/2, FLTP/4M and HRD16) and Quad Mode (qsim, qf) are controlled by the RCU. For the SADC, HADC, HADC/2 and HRD16 the information is sent directly over the 50 way digitizer cable. For the FLTP/4M the information is sent through the SADC, HADC or HADC/2 to the FLTP/4M via the I2C Bus of the AQR backplane.

- 6. For homodecoupling the timing of the decoupling pulses is set by the RCU. The RCU generates two signals SPHD and EPHD.

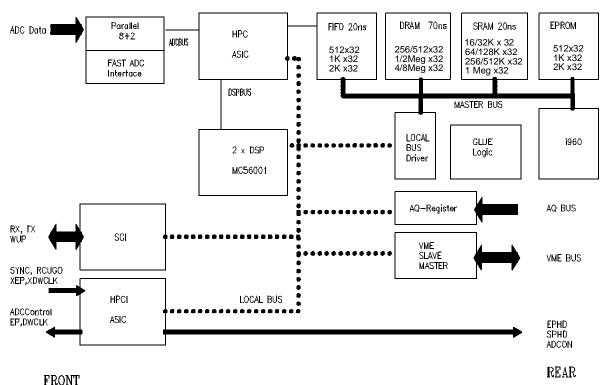

### AQX RCU overview

The RCU is a VMEBUS Board. All main functions are placed on the motherboard. In general the RCU is a VME Slave but it can also do some VME master DMA functions (transfer of FIDs to the acquisition computer).

The board consists of a i960 RISC CPU processor system with a boot eprom, a fast SRAM (0 Wait States, Pipelined) a larger DRAM (aquisition data memory) and a FIFO (data synchronisation). The so called masterbus section is exremly fast. The lower speed section (localbus) gives access to the VMEBUS, digital signal processors, DWELL clock generator (HPCI) and the debugging port (SCI). The interface to the ADC is done by a RS422 interface for low sampling (1MHz) AD converter system or an adequate fast ADC interface. The HPC checks the connection to the AD converter system and prepares the incomming data. A special communication register (AQ-Register) is placed on this board to get realtime instructions from the TCU (dummy scan, channel A & B function, ..).

The software for the RCU is downloaded by the aquisition computer system, and may be placed in SRAM or/and DRAM. The DSP software is then downloaded by the i960 to the DSP system.

2.4

### AQX Connection to SADC and HADC

For high resolution NMR purpose two AD converter systems called HADC and SADC have been designed. They differ only in AD converter specification and max. DWELL clock, but they have the same interface to the RCU (RS422). This interface is galvanically isolated from the analog part on the AD converter system. For immunity reasons, the RS422 twisted pair concept was chosen. So one signal is physically transferred by two wires and galvanically isolated at the HADC or SADC.

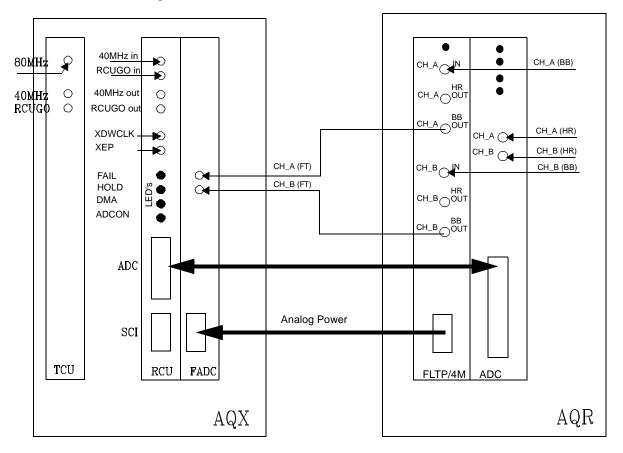

Figure 2.4. HR - System

As shown above, the RCU is located in the computer rack called AQX and the AD converter system (with the antialiasing filters) is located in the AQR rack. The only required connection is a 50 wire cable, that can be several meters long. The connection to TCU is made with the 40MHz and the RCUGO signal. For special purpose it is possible to connect an external DWELL CLOCK (XDWCLK) and external EP (XEP = Extern Empfaenger Puls) to the RCU.

### AQX Connection to FADC

For solids purpose an AD converter system called FADC has been designed. It is plugged directly onto the RCU. This interface is galvanically isolated from the analog part of the AD converter system. For technical reasons, the FADC is located in the computer rack AQX and not in the AQR. So the digitized signal is physically transferred by a short wire and galvanically isolated at the FADC.

Figure 2.5. Solid - NMR

As shown above, the FADC is located in the computer rack AQX but the corresponding antialiasing filter is located in the AQR rack. The power for the analog part of the FADC is supplied by the filterboard. A HADC or SADC must be placed to the system because the RCU controls the filterboard (FLTP/4M) via SADC or HADC. The filterboard delivers a analog signal based on the broadband input signals (BB) for the SADC/HADC (HR) high resolution input, if a direct HR signal from the receiver ist not available.

Note: The BB signals of the receiver are connected to the filterboard, and its BB output is connected to the FADC. The HR output of the receiver is always connected to the HADC or SADC directly. The HR output of the filterboard is optional and for testing purpose.

The SCI connector is an RS485 interface which can be used for debugging purposes. It is normally not used.

# Introduction AQS

3.1

### General AQS Version

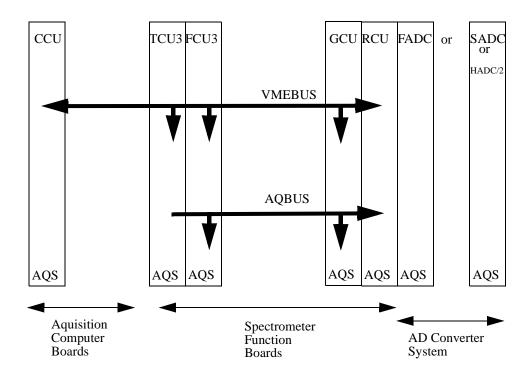

The Receiver Control Unit (RCU) is a member of the aquisition computer AQS. The AQS includes a complete aquisition computer system (i.e. CCU and the spectrometer specific function boards TCU3 (Timing Control Unit), FCU3 (Frequency Control Unit) and the mentioned RCU. The CCU includes also the fast memory and the SIO unit.

Figure 3.1. Aquisition system

An aditional AQBUS for the spectrometer function boards is used parallel to the VMEBUS. The RCU is the logical master for the AD converter system. It is the receiver of the data from the ADC System.

### System overview AQS Version

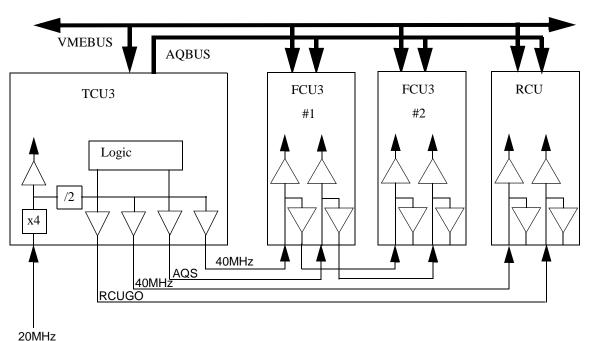

The aquisition computer is based on a VME system that uses a 32Bit Processor. So do all spectrometer function boards. Most spectrometer function boards have memory and local processors on board.

#### Figure 3.2. Spectrometer synchronisation

TCU:

- The TCU3 generates most RCP's (internal clock pulses) for the spectrometer. The main clock for the TCU3 is 80MHz derived from a 20MHz signal normally fed by a AQS REF RX22. Based on this clock, the FCU3's and the RCU realtime system run synchronous with 40MHz. So the time relation between the transmitter system (TCU3, FCU3) and the receiver system (RCU) is maintained. In special there are two strobe signals (AQS and RCUGO), triggering the spectrometer boards.

- 2. **20MHz:** This input signal comes directly from the AQS REF RX22 and is the clocking frequency for the TCU3. The voltage level is 0dBm (0,65Vpp at  $50\Omega$ ).This signal is used to generate the 40MHz signal.

- 3. **40MHz:** These output signals are TTL (3Vpp at  $50\Omega$ ) and operate on a 50% duty cycle. One is used to clock the FCU3's the other to clock the RCU.

- RCUGO: This pulse is used to start the RCU at every scan. It goes high for 50ns.

- AQBUS: Various instructions are sent from TCU3 to the FCU3's (and GCU if fitted) via the Acquisition Bus. This TTL strobe pulse is used to synchronise the timing of the bus. The strobe pulse goes low for a minimum of 25ns.

#### RCU:

- 1. The RCU takes complete control of the data acquisition. During the current scan it will operate autonomously until the end of the scan. To perform a second scan however the RCU must wait for a second RCUGO signal from the TCU3. The RCUGO signal is synchronised with the 40MHz clock, both are received from the TCU3.

- 2. The RCU is responsible for processing the acquired data (e.g. digital filtering) as well as accumulation and DMA transfer of processed data to the CCU.

- 3. The RCU is master of all digitizers (SADC, HADC/2 and FADC) and all digitizers functions. Also the filter settings (SADC, HADC/2 and FLTP/4M) and Quad Mode (qsim, qf and dqd) are controlled by the RCU. For the SADC and HADC/2 the information is sent directly over the 50 way digitizer cable. For the FLTP/4M the information is sent through the SADC or HADC/2 to the FLTP/4M via the I2C Bus of the AQS Adapter (Z003348).

### AQS RCU overview

The RCU is a VMEBUS Board. All main functions are placed on the motherboard. In general the RCU is a VME Slave but it can also do some VME master DMA functions (transfer of FIDs to the acquisition computer).

The board consists of a i960 RISC CPU processor system with a boot eprom, a fast SRAM (0 Wait States, Pipelined) a larger DRAM (aquisition data memory) and a FIFO (data synchronisation). The so called masterbus section is exremly fast. The lower speed section (localbus) gives access to the VMEBUS, digital signal processors, DWELL clock generator (HPCI) and the debugging port (SCI). The interface to the ADC is done by a RS422 interface for low sampling (1MHz) AD converter system or an adequate fast ADC interface. The HPC checks the connection to the AD converter system and prepares the incomming data. A special communication register (AQ-Register) is placed on this board to get realtime instructions from the TCU3 (dummy scan, channel A & B function, ...).

The software for the RCU is downloaded by the aquisition computer system, and may be placed in SRAM or/and DRAM. The DSP software is then downloaded by the i960 to the DSP system.

3.4

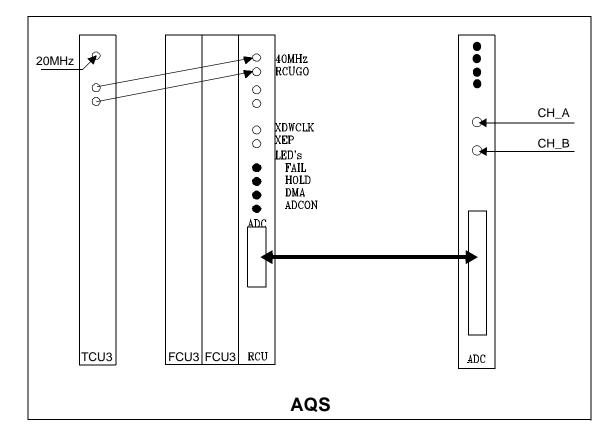

### AQS Connection to SADC and HADC

For high resolution NMR purpose two AD converter systems called HADC/2 and SADC have been designed. They differ only in AD converter specification and max. DWELL clock, but they have the same interface to the RCU (RS422). This interface is galvanically isolated from the analog part on the AD converter system. For immunity reasons, the RS422 twisted pair concept was chosen. So one signal is physically transferred by two wires and galvanically isolated at the HADC/2 or SADC.

Figure 3.4. HR - System

As shown above, the RCU is located in the computer rack called AQS and the AD converter system (with the antialiasing filters) is located in the same AQS rack. The only required connection is a 50 wire cable, that can be several meters long. The connection to TCU3 is made with the 40MHz and the RCUGO signal.

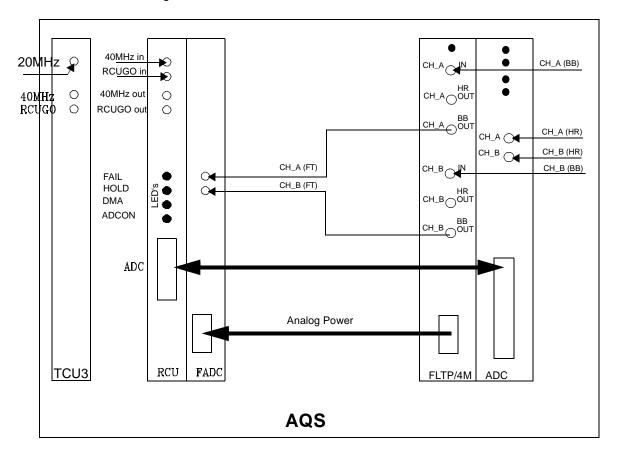

### AQS Connection to FADC

For solids purpose an AD converter system called FADC has been designed. It is plugged directly onto the RCU. This interface is galvanically isolated from the analog part of the AD converter system. So the digitized signal is physically transferred by a short wire and galvanically isolated at the FADC.

Figure 3.5. Solid - NMR

The power for the analog part of the FADC is supplied by the filterboard. A HADC/ 2 or SADC must be placed to the system because the RCU controls the filterboard (FLTP/4M) via SADC or HADC/2. The filterboard delivers a analog signal based on the broadband input signals (BB) for the SADC / HADC/2 (HR) high resolution input, if a direct HR signal from the receiver ist not available.

Note: The BB signals of the receiver are connected to the filterboard, and its BB output is connected to the FADC. The HR output of the receiver is always connected to the HADC/2 or SADC directly. The HR output of the filterboard is optional and for testing purpose.

# Installation

### General

4.2

The RCU is delivered with its factory settings. Under normal condition there is no need to modify anything. In case of troubles, the following information may be checked. There is also a testprogram (UNIX, aquisition computer) see also Chapter **4.9**.

This installation guide is adequate for P/N Z002488 ECL01..ECL06 and for Z003678 ECL00..01

(see separate Engineering Changes for details)

### **Technical data**

The RCU motherboard may be configured. The standard version is highlighted.

Aquisition Memory (DRAM) :1MByte/2MByte, **4MByte**/8Mbyte,16MByte/32MByte Fast Memory (SRAM) : **256/**512kByte, 1/2MByte, 4MByte FIFO Memory: **1kx9Bit**, 2kxBit, 4kxBit, 8kxBit Sampling Rate: max. 40MHz Power: 2.5A @ 5V Mechanical size: VMEBUS Board 6HE, Double extended (280mm), 4TE+

### Factory settings

4.3

The board is configured at factory as follows (see Jumper settings):

EPROM: 27C512 Clock Jumper: Inserted DRAM: 4MByte SRAM: 256KByte VME Interrupt: IRQ 3 VME Bus Request: BR3

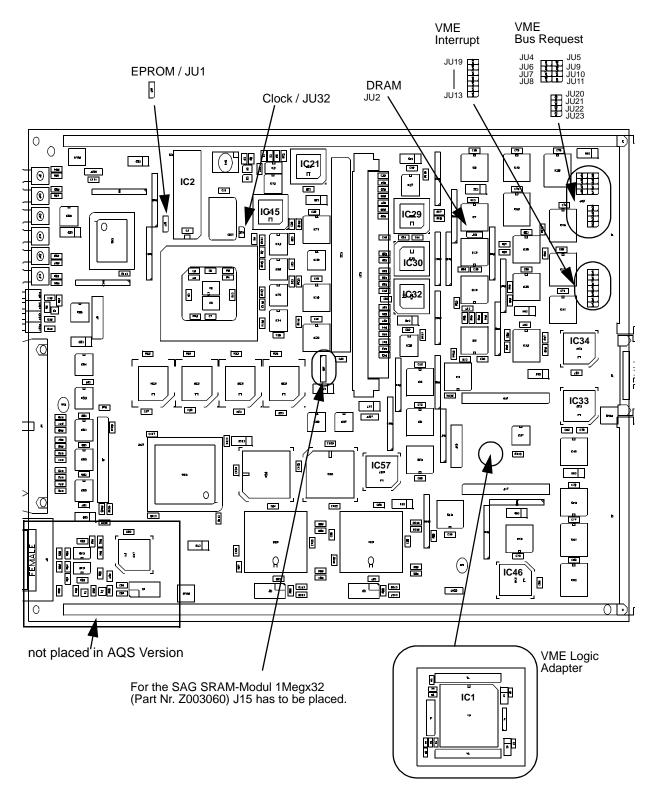

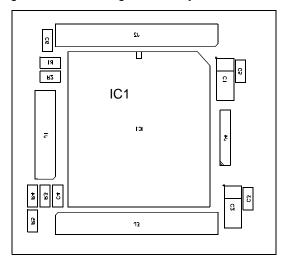

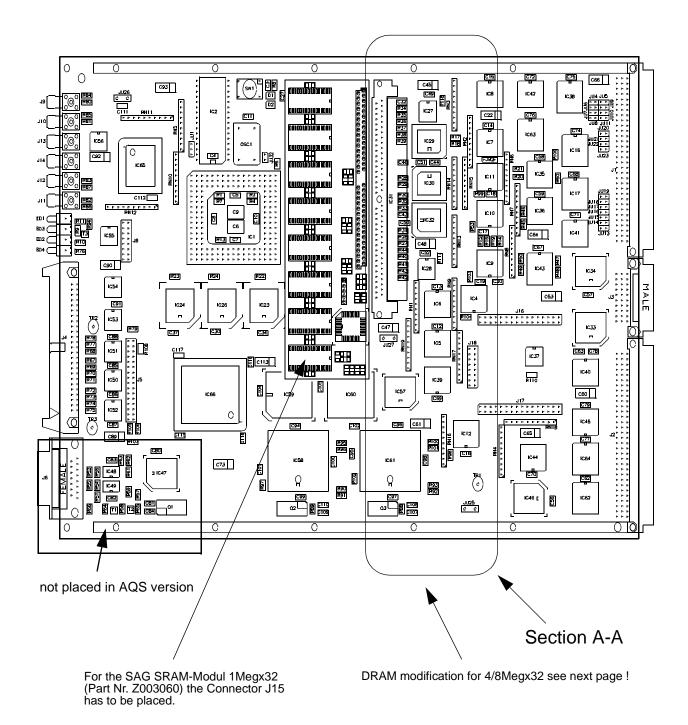

Figure 4.1. motherboard assembly

### Assembly VME logic board Z4P2925B

Figure 4.2. VME logic assembly

This board contains a complex logic device and controls the VME interface. It can be detached from the motherboard for exchange.

### Jumpersetting

#### **EPROM**:

4.6.1

The RCU supports in general two types of EPROM. JEDEC32 format (32 pin) and JEDEC format (28 pin). The EPROM must be inserted with upper boarder adjusted (*not pin 1*). At the moment there are two EPROMs defined.

#### Table 4.1.EPROM configuration

| EPROM    | SIZE/Type | JU1  |

|----------|-----------|------|

| RCU0AA01 | 256k      | up • |

| RCU0BB01 | 512k      | up • |

|          | 1M        | down |

| DRAM:        |                                     |   | 4.6.1 |

|--------------|-------------------------------------|---|-------|

|              | The Jumper JU32 has to be inserted. | • |       |

| Clock:       |                                     |   | 4.6.2 |

| Installation |                                     |   |       |

### The RCU supports four types of DRAM SIMM modules:

Table 4.2. DRAM configuration / Jumper settings

| DRAM             | SIZE              | JU2       |  |

|------------------|-------------------|-----------|--|

| 256K / 512K x 32 | 1MByte / 2MByte   | right ••• |  |

| 1M / 2M x 32     | 4MByte / 8MByte   | left •••  |  |

| 4M / 8M x 32     | 16MByte / 32MByte | not used  |  |

### VME Interrupt:

4.6.2

Changing of interrupt level needs a change in PAL RCU0AA09.

Table 4.3.

VME Interrupt configuration / Jumper settings

| LEVEL | JUMPER     |    |         |

|-------|------------|----|---------|

| IRQ1  | JU13 / Out | •• |         |

| IRQ2  | JU14 / Out | •• |         |

| IRQ3  | JU15 / Out | •• | default |

| IRQ4  | JU16 / Out | •• |         |

| IRQ5  | JU17 / In  | •• |         |

| IRQ6  | JU18 / Out | •• |         |

| IRQ7  | JU19 / Out | •• |         |

The VME Bus request can be choosen to 4 different levels. They are all implemented the same way, so only one level is explained. The BUS Request BR is granted by the VME Bus master with BGIN. If the board didn't request it, it has to propagate this grant with BGOUT. So there are 3 signals to handle. In the table the '\*' means to put one jumper between both jumper positions, the '&' to put each jumper.

### Table 4.4.VMEBUS Request configuration / Jumper settings

| LEVEL       | BR   | BG to RCU  | BG not to RCU               |  |

|-------------|------|------------|-----------------------------|--|

| 0           | JU20 | JU4 & JU5  | JU6*9,<br>JU7*10,<br>JU8*11 |  |

| 1           | JU21 | JU6 & JU9  | JU4*5,<br>JU7*10,<br>JU8*11 |  |

| 2           | JU22 | JU7 & JU10 | JU4*5,<br>JU6*9,<br>JU8*11  |  |

| 3 / default | JU23 | JU8 & JU11 | JU4*5,<br>JU6*9,<br>JU7*10  |  |

## Programmable logic

The RCU contains several programmable logic devices.

### Table 4.5. Programmable logic configuration

| Name     | Туре       | IC   | Remarks                          |

|----------|------------|------|----------------------------------|

| RCU0xx01 | EPROM 512k | IC2  | BOOT ROM CPU /4                  |

| RCU0xx02 | 85C220     | IC15 | Fast- & Reset                    |

| RCU0xx03 | 85C220     | IC21 | SRAM/FIFO                        |

| RCU0xx04 | 85C220     | IC29 | DRAM RAS                         |

| RCU0xx05 | 85C220     | IC30 | DRAM ADR                         |

| RCU0xx06 | 85C220     | IC32 | DRAM CAS                         |

| RCU0xx07 | plsi1032   | IC1* | VME (VME Logic Adapter)          |

| RCU0xx08 | 20L8A      | IC33 | VME Address decode high<br>CPU/4 |

| RCU0xx09 | 20L8A      | IC34 | VME Address Low                  |

| RCU0xx10 | 22V10      | IC46 | AQ-Register control              |

| RCU0xx11 | 20L8A      | IC57 | DSP Address decode               |

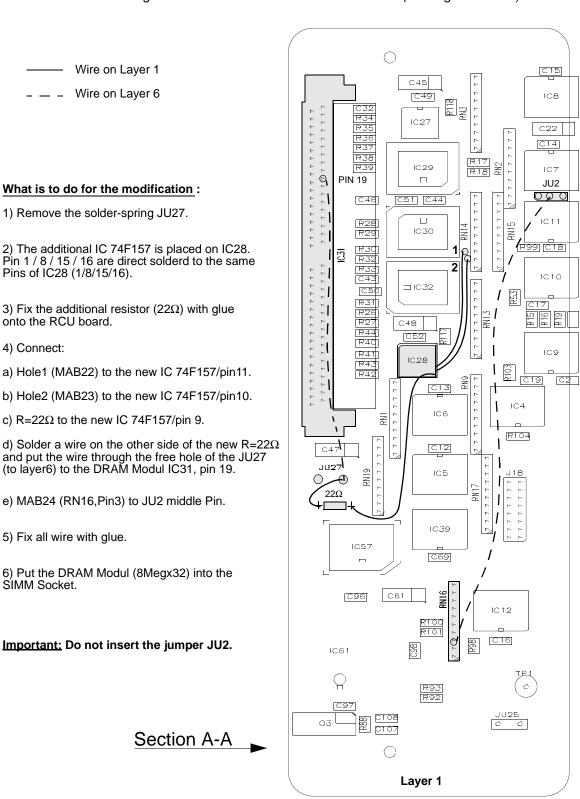

4.8

Extended Memory means: SRAM 1/2Meg x 32Bit / DRAM 4/8Meg x 32Bit

Figure 4.3. Assembly motherboard with extended memory

### Installation

Figure 4.4. Modification on the motherboard (4/8Megx32 DRAM)

### Testprogram

For the CPU/4, CCU aquistion computer a testprogram has been developed, which is on the standard BRUKER NMR (DMX, DRX,...series) software package. To use this, the following procedure is to be used:

- 1. Open a X Window

- 2. Connect to aquisition computer 'telnet spect'

- 3. Login as 'root'

- 4. Change to '*/etc/rcu*' (for older UXNMR versions) or to '*/u/systest/rcu*'

- 5. start testprogram with './rcutest'

- 6. Use help function '*h*' or autotest 'auto'

## ! Useful commands are:

"h" = help and prints a list of the commands

"res" = performs a software reset of the RCU

"auto" = starts the automatic self test

### **Configuration Test**

4.10

- 1. Open a X Window

- 2. Start UXNMR

- 3. Type : cf

Answer different questions and finally check the configuration information of the RCU. Technical data about the memory size see chapter <u>4.2</u>.

Table 4.6. Memory check list

| RCU  | memory size<br>{KByte}        |

|------|-------------------------------|

| DRAM | XXXX                          |

| SRAM | XXXX                          |

| FIFO | XXXX                          |

| ADC  | installed or<br>not installed |

# Installation

# Figures

| Conte       | nts                                                | 3  |

|-------------|----------------------------------------------------|----|

| 1 Gener     | al Infos                                           | 5  |

| 2 Introd    | luction AQX                                        | 7  |

| Figure 2.1. | Aquisition system                                  | 7  |

| Figure 2.2. |                                                    |    |

| Figure 2.3. | RCU Blockdiagram                                   |    |

| Figure 2.4. | HR - System                                        |    |

| Figure 2.5. | Solid - NMR                                        | 12 |

| 3 Introd    | luction AQS                                        | 13 |

| Figure 3.1. | Aquisition system                                  | 13 |

| Figure 3.2. | Spectrometer synchronisation                       | 14 |

| Figure 3.3. | RCU Blockdiagram                                   | 16 |

| Figure 3.4. | HR - System                                        | 17 |

| Figure 3.5. | Solid - NMR                                        | 18 |

| 4 Instal    | lation                                             | 19 |

| Figure 4.1. | motherboard assembly                               | 20 |

| Figure 4.2. | VME logic assembly                                 | 21 |

| Figure 4.3. | Assembly motherboard with extended memory          | 25 |

| Figure 4.4. | Modification on the motherboard (4/8Megx32 DRAM) . | 26 |

| Figure      | es                                                 | 29 |

| Tables      | S                                                  | 31 |

|             |                                                    |    |

# Figures

# **Tables**

|     | Contents   | \$                                             | 3  |

|-----|------------|------------------------------------------------|----|

| 1   | General    | Infos                                          | 5  |

| 2   | Introduc   | tion AQX                                       | 7  |

| 3   | Introduc   | tion AQS                                       | 13 |

| 4   | Installati | on                                             | 19 |

| Tab | ole 4.1.   | EPROM configuration                            | 21 |

| Tab | ole 4.2.   | DRAM configuration / Jumper settings           | 22 |

| Tab | ole 4.3.   | VME Interrupt configuration / Jumper settings  | 22 |

| Tab | ole 4.4.   | VMEBUS Request configuration / Jumper settings | 23 |

| Tab | ole 4.5.   | Programmable logic configuration               | 24 |

| Tab | ole 4.6.   | Memory check list                              | 27 |

|     | Figures    |                                                | 29 |

|     | Tables     |                                                | 31 |

## Tables

Notes